研究組織・メンバー

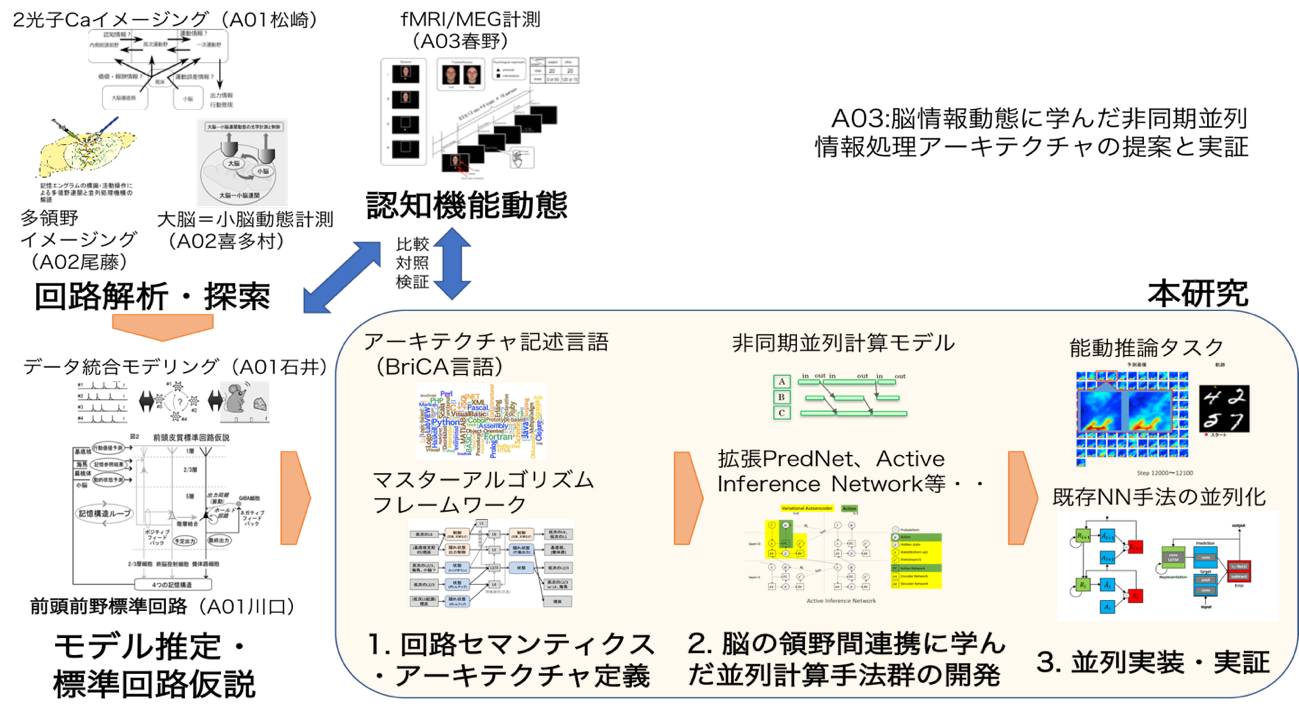

A03:脳情報動態に学んだ非同期並列情報処理アーキテクチャの提案と実証

研究代表者

研究代表者

高橋恒一・理化学研究所・チームリーダー

WEBhttp://lbcs.riken.jp

分担研究者

山川 宏・ドワンゴ人工知能研究所・所長/東京大学医学部・客員研究員

紹介文本文

脳は低速、低精度、低信頼性の情報処理素子である神経細胞が多数集合し、多階層の時空間動態を持つ超並列情報処理装置である。現状の人工神経回路では回路全体を誤差逆伝播法で学習する同期ボトルネックのため並列処理に足枷があり、その拡張性を著しく阻害している。本研究では、特に大脳新皮質の領野間結合様式に注目し、脳の時空間的に階層的な情報動態にヒントを得た非同期並列の情報処理アーキテクチャを提案、実装、実証する。

具体的には、A01班およびA02班が行う領野間回路解析・探索とモデル推定を統合した標準回路仮説に対し、本研究で(1)入出力回路セマンティクスとアーキテクチャ定義を付与してマスターアルゴリズムフレームワーク(MAF)として整備する。次に、(2)提案者らの研究グループが開発する基盤ソフトウエアBriCAを拡張し、多階層非同期並列計算モデル(あるモジュールが他のサブモジュールを包含する形で、全体として多数のモジュールが非同期的に矛盾なく並行実行されるような計算モデル)に対応させる。これを用いて、(3)いくつかの既存および新規の計算手法とそのMAFに準拠した拡張を実装し、能動推論タスクや並列化性能などをベンチマークとして性能評価を行う。

脳情報動態の時空間的階層性は現代の計算アーキテクチャのプロセッサ、メモリ、ネットワーク階層における局所性との共通点も多く、分散並列アーキテクチャの観点から脳に学べる点は多い。本研究は将来的にはエネルギー効率が飛躍的に高い情報処理技術やIoTなどの情報通信ネットワークの効率化、高信頼性などに結びつく可能性がある。

図1 本研究の流れと他班との関係

文献

- Reinterpreting The Cortical Circuit, Yamakawa H, Arakawa N, Takahashi K, Proceedings of the IJCAI-17 Workshop on Architectures for Generality & Autonomy, 2017.

- K. Itaya, *K. Takahashi, M. Nakamura, M. Koizumi, N. Arakawa, M. Tomita, & H. Yamakawa, BriCA: A Modular Software Platform for Whole Brain Architecture., ICONIP16, 10.1007/978-3-319-46687-3_37 (2016).

- Y. Shindo, K. Iwamoto, K. Mouri, K. Hibino, M. Tomita, H. Kosako, Y. Sako, &*K. Takahashi, Conversion of graded phosphorylation into switch-like nuclear translocation via autoregulatory mechanisms in ERK signalling., Nature Communications, 7, doi:10.1038/ncomms10485 (2016).

- K. Takahashi, K. Itaya, M. Nakamura, M. Koizumi, N. Arakawa, M. Tomita, & H. Yamakawa, A generic software platform for brain-inspired cognitive Computing., Proc. Comput. Sci, 71, 31-35 (2015).